### WERSINDWIR?

Mit mehr als 150 Kunden rund um den Globus Seit 2017 ist Sensor to Image Teil von Euresys ist Sensor to Image weltweit führender Antellen mit Unterstützung von GigE Vision, portnetzwerk der Gruppe. USB3 Vision und CoaXPress.

ren die Entwicklungszeit von Kameras und eingebetteten Systemen und sind gleichzeitig sehr leistungsstark bei geringem Platzbedarf. Sensor to Image arbeitet seit über 15 Jahren mit den Fachausschüssen für GigE Vision und USB3 Vision sowie GenlCam zusammen und ist seit 10 Jahren an der Entwicklung des Sensor to Image hat weltweit über 150 Kun-CoaXPress-Standards beteiligt.

gau (Deutschland) ist ein Spezialist im Bereich Machine Vision, der FPGA-basierte Imaging- und Video-IP-Cores und -Produkte bereichen zählen die Standards GenICam, GigE Vision, CoaXPress, USB3 Vision und MIPI sowie die AMD- und Intel-Plattformen kombiniert mit Hardware-Engineering und Produktionskenntnissen. Seit der Firmengründung 1989 hat sich das Unternehmen ein renommiertes Know-how bei modularen PC-Bildverarbeitungskarten aufgebaut.

und profitiert von der globalen Reichweite bieter von IP-Cores für industrielle Schnitts- und dem umfassenden Vertriebs- und Sup-

Heute sind die Hauptprodukte von Sensor to Image GigE Vision-, CoaXPress- und USB3 Die Lösungen von Sensor to Image minimie- Vision-IP-Cores sowie IMX Pregius- und MI-PI-IP-Cores. Sie sind mit AMD-, Intel- und Microchip PolarFire-FPGAs kompatibel. Seine Vision-Standard IP-Cores sind A3- und JIIA-zertifiziert und Sensor to Image ist ein aktives Mitglied dieser Verbände.

den in den Anwendungsbereichen Automobile, Industrie, Medizin, Sicherheit, Militär Die Sensor to Image GmbH mit Sitz in Schon- und Raumfahrt beliefert. Sensor to Image ist Mitglied des AMD- und Microchip-Partnerprogramms sowie ein Intel-Lösungspartner.

Was auch immer der Vision-Standard (CoaXentwickelt und verkauft. Zu seinen Fach- Press, GigE Vision, USB3 Vision, ...) und Bildsensor (Sony IMX Pregius, MIPI CSI-2 ...) Ihrer Wahl ist - Sensor to Image hat wahrscheinlich die Bausteine für Ihr Machine-Vision-Projekt.

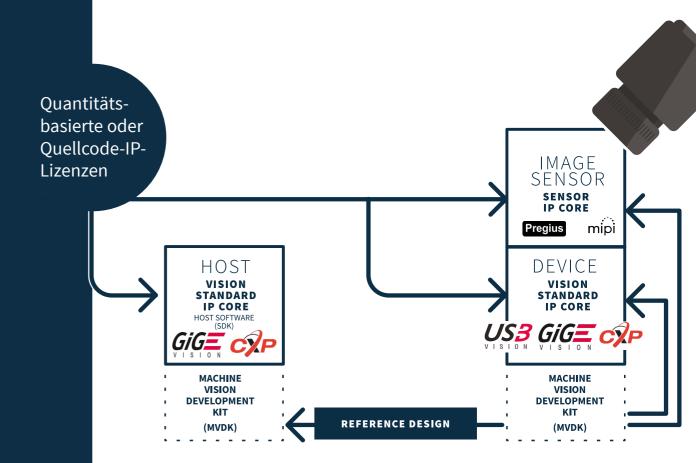

### IP-Core-Konzept

IP-Cores werden bei der FPGA-Entwicklung häufig verwendet, um bewährte Funktionen in einem Design zu integrieren. Sie reduzieren die Entwicklungszeit und erhöhen die Designqualität, vor allem bei komplexen Designs.

Die IP-Cores von Sensor to Image für die GigE Vision-, USB3 Vision- und CoaXPress-Transportschichten sowie die SubLVDS- und MIPI-CSI2-Sensorschnittstellen sind so konzipiert, dass sie Kunden bei der Entwicklung ihrer eigenen Vision-Komponenten unterstützen.

Ein typisches Device-Design besteht aus mehreren Funktionsblöcken sowie IP-Cores vom FPGA-Anbieter. Die Architektur kann komplex sein und der Entwickler muss sich gut mit dem FPGA und der Firmware auskennen.

Damit die Integration der IP-Cores von Sensor to Image vereinfacht wird, bieten wir ein vollständig funktionierendes Referenzdesign für eine Evaluierungsplattform an, die der Zielplattform so ähnlich wie möglich ist. Diese Referenzdesigns beschleunigen die Integration und reduzieren Entwicklungskosten.

#### Vision-Standard-Software

USB3 & GIGE VISION

AUF EINEN BLICK

- Host-Software-SDK für GigE Vision und USB3 Vision

- GigE Vision-Kamerasimulator

- Kompatibel mit Windows und Linux

- Als Quellcode verfügbar

### Flexible Lizenzmodelle für IP-Cores

Sensor to Image gewährt zur Verwendung seiner Intellectual Property (IP) Lizenzen. Je nach Anwendungsfall gibt es unterschiedliche Lizenzmodelle. Lizenzen werden in der Regel als "Projektlizenz" vergeben, das heißt:

- eine FPGA-Familie

- ein dediziertes Designteam

- die Änderung einer FPGA-Familie erfordert ein "Projekt-Upgrade"

- · Multi-Projekt-Lizenzen sind zu einem höheren Preis und einigen Support-Einschränkungen möglich

Je nach Produktionsvolumen und Designkomplexität sind folgende Lizenzmodelle möglich:

- eine Einzellizenz, einschließlich einem "encrypted VHDL" IP-Core. Dieses Lizenzmodell bietet die niedrigsten Anschaffungskosten, hat aber wiederkehrende Kosten für die Lizenzchips, die direkt von S2I erworben werden. Dieses Modell ist die "Starter Edition" und geeignet für ein Design, das einem Standard-Referenzdesign sehr ähnlich ist, sowie geringe Produktionsmengen. Nicht alle Features einer IP werden von diesem Modell unterstützt.

- eine Volumenlizenz, einschließlich mehr Supportoptionen, geringeren Kosten für Lizenzchips (falls erforderlich) und gegebenenfalls VHDL-Quellcode. Volumen- und Upgrade-Rabatte sind verfügbar. Dieses Modell ist die "Professional Edition" und geeignet für komplexe Designs oder höhere Produktionsmengen.

Optionale Wartungsverträge gewährleisten, dass die IP immer auf dem neusten Stand ist und langfristiger Support besteht.

© EURESYS S.A. Subject to change without notice

### Machine-Vision-**Standards**

Technologiestandards helfen dabei, den Markt zu vereinfachen und die Komplexität für spezielle Technologien zu verringern. In der Machine-Vision-Branche sind Standards zum Vergleichen von Produkten verschiedener Anbieter hilfreich. Außerdem ermöglichen Sie Kompatibilität und eine breite Marktakzeptanz.

In den letzten 20 Jahren wurden in der Branche mehrere neue digitale Standards entwickelt und gepflegt, um dem wachsenden Spektrum an Anwendungsfällen gerecht zu werden.

Transportschichten-Standards bieten Zugriff auf die Kamera-Register und definieren Datenstreams für Bilder und andere Daten.

Hier die wichtigsten Transportschichten-Standards, für die Sensor to Image IP-Cores empfiehlt:

#### **GigE Vision**

GigE Vision ist ein globaler Kameraschnittstellen-Standard der anhand des Gigabit Ethernet-Kommunikationsprotokolls entwickelt wurde. GigE Vision ermöglicht eine schnelle Bildübertragung über günstige Standardkabel über sehr lange Kabellängen. Mit GigE Vision ist Hardware und Software verschiedener Anbieter nahtlos über GigE-Verbindungen miteinander kompatibel.

GigE Vision ist eine auf der ganzen Welt gängige Schnittstelle und Dutzende führender Unternehmen bieten derzeit Hunderte von Produkten an, die mit GigE Vision konform sind. GigE Vision bietet viele Vorteile, darunter:

- SCHNELL: Hohe Bandbreiten (115 MiB/s @ 1 Gbit/s, 1150 MiB/s @ 10 Gbit/s) übertragen große Bilder schnell in Echtzeit

- WEITREICHEND: Hervorragende Datenübertragung über eine Länge von bis zu 100 Meter über Kupferkabel oder noch länger über Glasfaser

- **STANDARD:** Günstige CAT5e- oder CAT6-Kabel und Standardanschlüsse

- SKALIERBAR: Hoch skalierbar für das schnelle Wachstum von Ethernet

- **GÜNSTIG:** Standardhardware und -kabel ermöglichen eine einfache, günstige Integration

#### **USB3 Vision**

Die USB3 Vision-Schnittstelle basiert auf der standardmäßigen USB 3.x-Schnittstelle. mit der alle aktuellen PCs und viele eingebettete Systeme ausgestattet sind. Kameras und andere Geräte, die diesen Standard verwenden, sind mit einer breiten Palette an Produkten vieler Anbieter kompatibel.

- Hohe Bandbreite und geringer Performance-Overhead

- Benutzerfreundliche Plug-and-play-Schnittstelle

- Stromversorgung und Datenübertragung über dasselbe passive Kabel bis zu 5 Meter (länger mit aktiven Kabeln)

#### **CoaXPress**

Die digitale CoaXPress-Schnittstelle wurde für Bilddatenübertragungen mit hoher Geschwindigkeit entwickelt und ist vor allem für Machine-Vision-Anwendungen gedacht. Die Schnittstelle eignet sich auch für andere Imaging-Anwendungen und für sehr schnelle Datenübertragungen in anderen Bereichen. CoaXPress verwendet als physisches Medium Koaxialkabel und unterstützt seit Kurzem auch optische Kabel.

CoaXPress wird von der JIIA (Japan Industrial Imaging Association) gehostet. Die Fachausschüsse für CoaXPress der JIIA sind für die Vorbereitung und Pflege des Standards zuständig. Beiträge kommen auch vom CoaXPress Consortium und der CoaXPress Liaison Group, also für Mitglieder der A3 und EMVA.

#### CoaXPress-over-Fiber

Das CoaXPress-over-Fiber-Konzept basiert auf der Topologie des physischen Mediums Ethernet und auf einer Reihe von Regeln zur Zuordnung des CoaXPress-Protokolls zur Schnittstelle der physischen Ethernet-Schicht. Basierend auf diesen Regeln wird eine CXP-PHY-Bridge (CoaXPress to Ethernet Physical Layer Bridge) spezifiziert, sodass das CoaXPress-Protokoll über verfügbare vorhandene Ethernetkomponenten transportiert werden kann, ohne dass neue Glasfaserkomponenten für den CoaXPress-Standard erforderlich sind.

(Quelle: automate.org & jiia.org)

#### **GenICam**

GenICam ist eine globale Reihe von Standards, die als Schnittstelle zwischen Kameras und Softwareanwendungen auf Computern dienen. GenlCam ermöglicht die Homogenisierung der Bezeichnungen, Schnittstellen und Prozesse in Bildverarbeitung, Erfassung und Transport. Durch gemeinsame Bezeichnungen und Konfigurationen gewährleistet GenICam die Kommunikation unabhängig von Implementierungsdetails des Anbieters, Funktionen oder Schnittstellentechnologie. GenICam ist die Basis für Videostandards wie GigE Vision, USB3 Vision, CoaXPress und Camera Link.

Sensor to Image bietet Entwicklern Produkte, um ihnen die Entwicklung von Devices und Software leichter zu machen. Dafür bieten wir eine breite Palette an FPGA-IP-Cores und SDKs an, die auf den folgenden Seiten aufgeführt sind.

© EURESYS S.A. Subject to change without notice

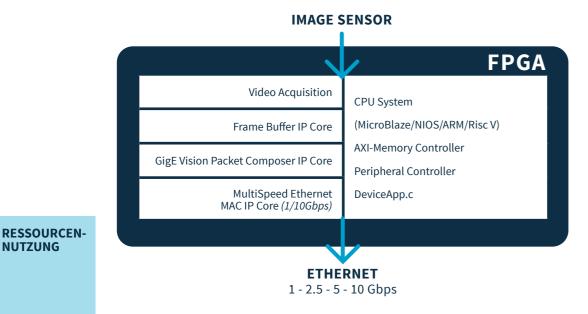

## GigE Vision Device **IP** Core

GigE Vision Device IP Core für FPGA

- · Mit Bauteilen der AMD 7-Serie (und höher) und Intel Cyclone V-Devices (und höher) kompatibel

- Vorab kompatibel mit Microchip PolarFire

- Kompakt, anpassbar

- Unterstützt Geschwindigkeiten von 1 Gbit/s bis über 10 Gbit/s

- · Lieferung als funktionierendes Referenzdesign

#### Beschreibung vom GigE Vision-IP-Core

GigE Vision ist ein Standard-Kommunikationsprotokoll für Vision-Anwendungen basierend auf der bekannten Ethernet-Technologie. Dieser Standard ermöglicht einfache Verbindungen zwischen GigE Vision-Devices und PCs, die ein Protokoll der TCP/IP-Familie ausführen. Sensor to Image bietet eine Reihe von IP-Cores und ein Entwicklungsframework für die Entwicklung von FPGA-basierten Transmitterprodukten mit GigE Vision-Schnittstelle an. Aufgrund der Geschwindigkeit von GigE Vision, insbesondere bei Geschwindigkeiten über 1 Gbit/s, benötigen Sender eine schnelle FPGA-basierte Implementierung des integrierten GigE-Core. Die Reihe von GigE Vision-Cores ist mit Bauteilen der AMD 7-Serie (und höher), Intel Cyclone V-Devices (und höher) und der Microchip PolarFire-Serie kompatibel.

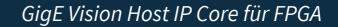

## GigE Vision Host **IP** Core

- Mit Bauteilen der AMD 7-Serie (und höher) und Intel Cyclone V-Devices (und höher) kompatibel

- Kompakt, anpassbar

- Unterstützt Geschwindigkeiten von 1 Gbit/s bis über 10 Gbit/s

- · Lieferung als funktionierendes Referenzdesign

#### Beschreibung des GigE Vision Host-IP-Cores

GigE Vision ist ein Standard-Kommunikationsprotokoll für Vision-Anwendungen basierend auf der bekannten Ethernet-Technologie. Dieser Standard ermöglicht einfache Verbindungen zwischen GigE Vision-Devices und PCs, die ein Protokoll der TCP/IP-Familie ausführen. Sensor to Image bietet eine Reihe von IP-Cores und ein Entwicklungsframework für die Entwicklung von FPGA-basierten Empfängerprodukten mit GigE Vision-Schnittstelle an. Aufgrund der Geschwindigkeit von GigE Vision, insbesondere bei Geschwindigkeiten über 1 Gbit/s, benötigen Empfänger eine schnelle FPGA-basierte Implementierung des integrierten GigE-Core. Die Reihe von GigE Vision-Cores ist mit AMD-Bauteilen und Intel-Devices

**NUTZUNG**

# GigE Vision Host Software

Software Development Kit für GigE Vision-kompatible Anwendungen

#### **AUF EINEN BLICK**

- Mit GigE Vision und GenICam kompatibles SDK

- Mit Windows- und Linux- Betriebssystemen kompatibel

- Unterstützung für x86 und ARM32/64

- · Quellcode erhältlich

#### Beschreibung des Sphinx GigE Vision Transportschicht-SDK

Sensor to Image bietet ein Software-Toolkit mit allen erforderlichen Funktionen für die schnelle, unkomplizierte Entwicklung von hochleistungsfähigen Bilderfassungsanwendungen.

Dieses Softwarekit umfasst mehrere Komponenten:

Der Sphinx GigE Vision Viewer ist eine Desktop-Anwendung zum Entdecken und Konfigurieren von GigE Vision-kompatiblen Kameras. Er empfängt auch GigE Vision-Streams und zeigt sie an.

Eine Transportschicht-Bibliothek (Sphinx GigE Vision-Bibliothek) implementiert alle spezifischen Aufgaben der Lower-Level-Transportschicht und enthält entweder eine intuitive proprietäre API oder fungiert mit der GenTL-konformen Schnittstelle als GenTL Producer.

Für die Leistungsoptimierung wird ein Filtertreiber geliefert, der die CPU-Last verringert und die Systemstabilität erhöht.

Das Sphinx GigE Vision SDK unterstützt alle obligatorischen und die meisten der optionalen Features, die nach der GigE Vision-Spezifikation bis einschließlich Version 2.2 definiert sind. Sowohl Windows- als auch Linux-Betriebssysteme werden unterstützt.

Je nach Lizenz werden die Komponenten des SDK teilweise oder vollständig als C-Quellcode geliefert.

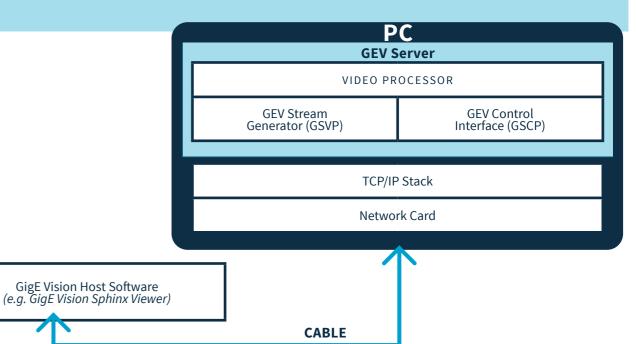

### GigE Vision Server

Software-basierte GigE Vision-Device-Implementierung

#### **AUF EINEN BLIC**

- Mit GigE Vision und GenICam kompatibles SDK zum Emulieren von GigE Vision-Transmittern

- Mit Windows- und Linux- Betriebssystemen kompatibel

- Unterstützung für x86 und ARM32/64

- Lieferung des vollständigen Quellcodes

#### Beschreibung des Sphinx GigE Vision-SERVERS

Das Softwarepaket für den GigE Vision-Server dient zum Erstellen von softwarebasierten GigE Vision-Geräteanwendungen. Dies ist für die softwarebasierte GigE Vision-Emulation oder für CPU-basierte Devices nützlich, die keine hohen Datenraten erfordern (für diese Anwendungen siehe den FPGA IP Core), oder für die Prototypenentwicklung von GigE Vision-Devices. Mit dem Paket ist es möglich, GigE Vision 1.x- oder 2.x-kompatible Devices für Windows- oder Linux-Betriebssysteme zu designen. Der Server wird mit vollständigem C-Quellcode geliefert. Daher ist die Erweiterung mit spezifischen Features möglich.

12

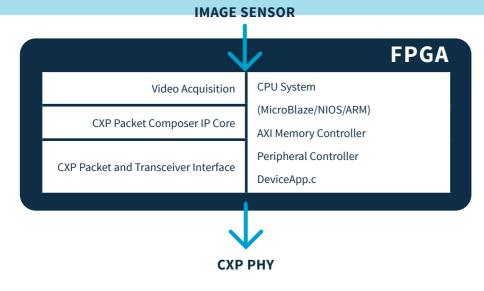

### CoaXPress Device IP Core

CoaXPress Device IP Core für FPGA

#### **AUF EINEN BLICK**

- · Mit Bauteilen der AMD 7-Serie (und höher), Intel Cyclone 10-Devices (und höher) kompatibel

- Vorab kompatibel mit Microchip PolarFire

- · Kompakt, anpassbar

- Unterstützt Geschwindigkeiten von 1 Gbit/s bis über 50 Gbit/s

- Funktionierendes Referenzdesign ist im Lieferumfang enthalten

#### Beschreibung des CoaXPress-IP-Cores

CoaXPress (CXP) ist ein Standard-Kommunikationsprotokoll für Vision-Anwendungen auf Basis der weit verbreiteten Koaxialkabel. Es dient als einfache Schnittstelle zwischen Kameras und Framegrabbern und unterstützt den Softwarestandard GenICam. Sensor to Image bietet eine Reihe von IP-Cores und ein Entwicklungsframework für die Entwicklung von FPGA-basierten Transmittern mit CoaXPress-Schnittstelle. Aufgrund der Geschwindigkeit von CXP benötigen Sender eine schnelle FPGA-basierte Implementierung des integrierten CXP-Core unter Verwendung von integrierten Transceivern. CXP-Cores sind mit Bauteilen der AMD 7-Serie (und höher), Intel Cyclone 10-Devices (und höher) und der Microchip PolarFire-Serie kompatibel.

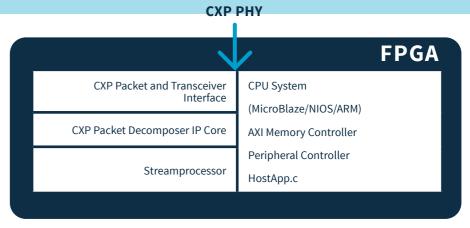

#### **AUF EINEN BLICK**

- Mit Bauteilen der AMD 7-Serie (und höher), Intel Cyclone 10-Devices (und höher) kompatibel

- Kompakt, anpassbar

- Unterstützt Geschwindigkeiten von 1 Gbit/s bis über 50 Gbit/s

- · Lieferung als funktionierendes Referenzdesign

#### Beschreibung des CoaXPress Host-IP-Cores

CoaXPress (CXP) ist ein Standard-Kommunikationsprotokoll für Vision-Anwendungen auf Basis der weit verbreiteten Koaxialkabel. Er dient als einfache Schnittstelle zwischen Kameras und Framegrabbern oder eingebetteten Prozessoren und unterstützt den Softwarestandard GenlCam. Sensor to Image bietet eine Reihe von IP-Cores und ein Entwicklungsframework für die Entwicklung von FPGA-basierten Empfängern mit CoaXPress-Schnittstelle. Aufgrund der Geschwindigkeit von CXP benötigen Empfänger eine schnelle FPGA-basierte Implementierung des integrierten CXP-Core unter Verwendung von integrierten Transceivern. Der CXP-Host-Core ist mit AMD-Bauteilen und Intel-Devices kompatibel.

RESSOURCEN-NUTZUNG

**RESSOURCEN-**

**NUTZUNG**

CoaxPress

over-Fiber

CoaxPress

over-Fiber

CoaxPress

over-Fiber

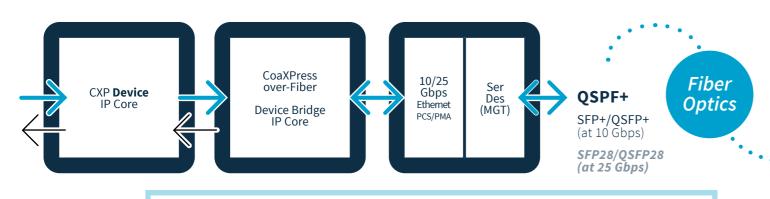

Device

Bridge IP Core

#### **AUF EINEN BLICK**

- CXP zu nGMII Bridge IP Core

- Kompatibel mit der AMD-Serie 7 (und neuer), Intel Cyclone 10 / Arria 10 / Agilex

- Mit CoaXPress Device IP Cores von S2I und Drittanbietern kompatibel

- Lieferung als funktionierendes Referenzdesign (sofern mit dem CoaXPress Device IP Core von S2I lizenziert) und umfassende Testbench zur Simulation

#### Beschreibung des CoaXPress-over-Fiber Bridge-IP-Core

Der CoaXPress-over-Fiber Device Bridge IP Core ermöglicht den Anschluss eines CoaXPress Device IP Cores an einen nGMII-Bus (10/25 Gbit/s Media Independent Interface) innerhalb eines FPGA. nGMII ist nach der Definition der IEEE-Norm 802.3, Klausel 46, der Hauptzugang zur physischen 10/25 G Ethernet-Schicht. Die allgemeinen Merkmale dieser Schnittstelle erleichtern das Mapping der CoaXPress-Signale auf die PCS/PMA-Ethernet-Unterschichten. Der IP-Core konvertiert CoaXPress-Steuerungs- und Streamingpakete in nGMII-Pakete, die an einen Ethernet-PCS/PMA-Block weitergeleitet werden.

#### Was ist CoaXPress-over-Fiber?

CoaXPress-over-Fiber ist eine kleine, aber signifikante Erweiterung der bestehenden CoaXPress-Spezifikation zur Unterstützung von Übertragungen über Glasfaser. CoaXPress (CXP) ist der De-facto-Standard für Computer-Vision-Anwendungen mit hoher Bandbreite. CoaXPress 2.1, die neueste Version der Spezifikation, spezifiziert die CXP-12-Geschwindigkeit, eine Verbindung mit 12,5 Gbit/s (Gigabit pro Sekunde) über ein koaxiales Kupferkabel. Da Link Aggregation bei CoaXPress üblich ist, sind mit vier CXP-12-Verbindungen problemlos Bandbreiten von 50 Gbit/s (12,5 x 4) möglich. CoaXPress-over-Fiber wurde als Ergänzung zur CoaXPress-Spezifikation entwickelt. Sie bietet eine Möglichkeit, das CoaXPress-Protokoll unverändert, also so wie es ist, über eine Standard-Ethernet-Verbindung einschließlich Glasfaser auszuführen. CoaXPress-over-Fiber verwendet dabei für Ethernet ausgelegte Standard-Elektronik, -Anschlüsse und -Kabel, wobei allerdings ausschließlich das CoaXPress-Protokoll, also weder das Ethernet- noch das GigE Vision-Protokoll, zum Einsatz kommt.

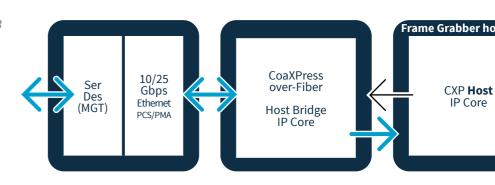

CoaXPress over-Fiber Host Bridge IP Core

CoaXPress-over-Fiber Host Bridge IP-Core für FPGA

#### **AUF EINEN BLICK**

- nGMII zu CXP Bridge IP Core

- Mit der AMD-Serie 7 (und höher) und Intel Cyclone/Arria 10/Agilex kompatibel

- Mit CoaXPress Host IP Cores von S2I und Drittanbietern kompatibel

- Lieferung als funktionierendes Referenzdesign (sofern mit dem CoaXPress Host IP Core von S2I lizenziert) und umfassende Testbench zur Simulation

#### Beschreibung des CoaXPress-over-Fiber Bridge-IP-Core

Der CoaXPress-over-Fiber Host Bridge IP Core ermöglicht den Anschluss eines CoaXPress Host IP Cores an einen nGMII-Bus (10/25 Gbit/s Media Independent Interface) innerhalb eines FPGA. nGMII ist nach der Definition in der IEEE-Norm 802.3 Klausel 46 der Hauptzugang zur physischen 10/25 G Ethernet-Layer. Die allgemeinen Merkmale dieser Schnittstelle erleichtern das Mapping der CoaXPress-Signale auf die PCS/PMA-Ethernet-Unterschichten. Der IP-Core konvertiert von einem Ethernet-PCS/PMA-Block empfangene nGMII-Pakete zurück in CoaXPress-Pakete.

SFP28/QSFP28 (at 25 Gbps) SFP+/QSFP+ (at 10 Gbps) QSPF+

#### Was sind die Vorteile der Verwendung von CoaXPress-over-Fiber für meine Anwendung?

- Verfügbar als CXP zu nGMII (Device) oder nGMII zu CXP (Host) Bridge IP Cores

- Ultrahohe Daten-/Frameraten

- Viele Zubehör- und Verkabelungsoptionen zur Abdeckung beliebiger Längenanforderungen

- Geringer CPU-Overhead, niedrige Latenz, jitterarme Bilderfassung

- Höchste Anzahl an Kameras pro PC-Leistung

- Sehr wettbewerbsfähiges Preis-Leistungs-Verhältnis

- Breite Branchenakzeptanz durch JIIA-Standardisierung

- Für CXP25 geeignet

**RESSOURCEN-**

**NUTZUNG**

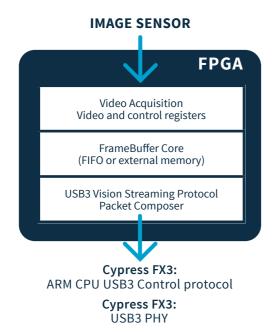

# USB3 Vision Device IP Core

USB3 Vision Device IP-Core für FPGA

#### **AUF EINEN BLICK**

- Mit Bauteilen der AMD 7-Serie (und höher) und Intel Cyclone V-Devices (und höher) kompatibel

- · Kompakt, anpassbar

- Lieferung als funktionierendes Referenzdesign

#### Beschreibung vom USB3 Vision-IP-Core

USB3 Vision ist ein Standard-Kommunikationsprotokoll für Vision-Anwendungen basierend auf der weitverbreiteten USB 3.0-Schnittstelle. Da es sich um ein Standardprotokoll handelt, das GenlCam unterstützt, ist eine einfache Verbindung zwischen Kameras und PCs möglich. Sensor to Image bietet eine Reihe von IP-Cores und ein Entwicklungsframework für die Entwicklung von FPGA-basierten Produkten mit USB3 Vision-Schnittstelle. Aufgrund der Geschwindigkeit von USB3 Vision benötigen Sender und Empfänger eine schnelle FPGA-basierte Implementierung des integrierten USB-Cores. USB3 Vision IP Cores sind mit Bauteilen der AMD 7-Serie (und höher) und Intel Cyclone V-Devices (und höher) kompatibel.

#### **AUF EINEN BLICK**

- Mit USB3 Vision und GenICam kompatibles SDK

- Mit Windows- und Linux- Betriebssystemen kompatibel

- Quellcode erhältlich

#### Beschreibung des Sphinx USB3 Vision Transportschicht-SDKs

Sensor to Image bietet ein Software-Toolkit mit allen erforderlichen Funktionen für die schnelle, unkomplizierte Entwicklung von hochleistungsfähigen Bilderfassungsanwendungen.

Dieses Softwarekit umfasst mehrere Komponenten:

Der Sphinx USB3 Vision Viewer ist eine Desktop-Anwendung zum Entdecken und Konfigurieren von USB3-kompatiblen Kameras. Er empfängt auch USB3 Vision-Streams und zeigt sie an.

Eine Transportschicht-Bibliothek (Sphinx USB3 Vision-Bibliothek) implementiert alle spezifischen Aufgaben der Lower-Level-Transportschicht und enthält entweder eine intuitive proprietäre API oder fungiert als GenTL Producer mit der GenTL-konformen Schnittstelle.

Die Software wird mit einem anpassbaren Treiber der USB3 Vision-Klasse geliefert.

Das Sphinx USB3 Vision SDK unterstützt alle obligatorischen und die meisten der optionalen Features, die nach der USB3 Vision-Spezifikation bis zur Version 1.2 definiert sind. Sowohl Windows- als auch Linux-Betriebssysteme werden unterstützt

Je nach Lizenz werden die Komponenten des SDK teilweise oder vollständig als C-Quellcode geliefert.

### **Pregius**

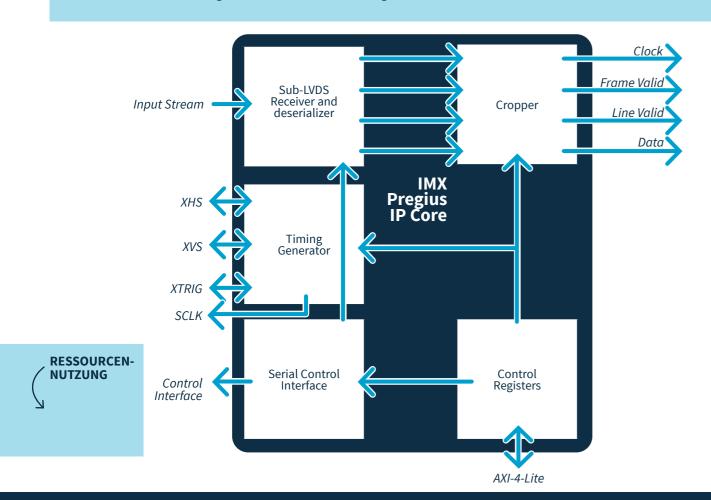

### IMX Pregius IP Core

*IP-Core für Sony Pregius Sub-LVDS-Bildsensoren*

#### **AUF EINEN BLICK**

- Readout- und Decoding-Block für Sub-LVDS

- SPI-basiertes Sensorkonfigurationsmodul

- Softwarebibliothek zur Sensorkonfiguration

- Freilaufende oder ausgelöste Readout-Modi

#### Beschreibung vom IMX Pregius-IP-Core

IMX Pregius von Sony ist eine Serie weitverbreiteter hochwertiger CMOS-Bildsensoren. Der IMX Pregius IP Core von S2I unterstützt diese Sensoren und kann ihre Daten lesen sowie auch steuern. Er wird als vollständig funktionierendes Referenzdesign geliefert und auf einer vereinbarten gemeinsamen Bereitstellungsplattform zusammen mit einem FMC-Modul ausgeführt, welches mit dem MVDK von S2I und FPGA-Standardevaluierungskits kompatibel ist. Zusammen bieten sie eine einfache Möglichkeit, eine Kamera zu designen.

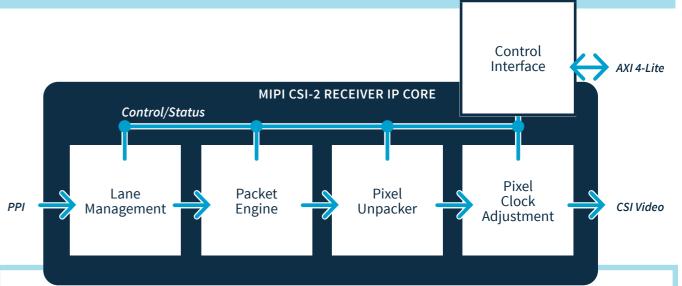

# MIPI CSI-2 Receiver IP Core

*IP-Core für MIPI CSI-2-Imager*

#### **AUF EINEN BLICK**

- MIPI CSI-2 Receiver- und Decoding-Block

- Konfigurierbare Anzahl an MIPI-Leitungen

- Mit AMD D-PHY IP

- Lieferung als funktionierendes Referenzdesign für schnelle Entwicklungen

#### Beschreibung vom MIPI CSI-2-IP-Core

Bildsensoren mit MIPI-Schnittstelle werden nicht nur in Mobiltelefonen verwendet, sondern auch in Industrie- und Automobilanwendungen. Viele dieser Anwendungen erfordern ein FPGA für die Steuerung und weitere Verarbeitung. Dieser IP-Core unterstützt die Vernetzung von MIPI-Sensoren anderer Anbieter mit FPGAs. Der IP-Core basiert auf einer vorhandenen D-PHY-Implementierung, die in der Regel bei FPGA-Anbietern erhältlich ist. Der IP-Core wird als vollständig funktionierendes Referenzdesign geliefert. Dieses wird auf einer vereinbarten gemeinsamen Bereitstellungsplattform zusammen mit einem MIPI-FMC-Modul ausgeführt, welches mit dem MVDK von S2I und FPGA-Standardevaluierungskits kompatibel ist. Zusammen bieten sie eine einfache Möglichkeit, eine Kamera zu designen.

#### Wichtigste Funktionen

- Unabhängig von FPGA-Technologie

- PPI-Schnittstelle zum Anschluss an verschiedene D-PHY-Implementierungen

- Konfigurierbar für 1, 2 oder 4 Datenleitungen

- Alle Leitungsgeschwindigkeiten (begrenzt durch das verwendete FPGA)

- RAW8, RAW10, RAW12, RAW14, RAW16 Standard-MIPI-Datentypen

- Eingebettete Datendekodierung

- Direkte Ausgabe von sortierten Bytestreams ohne Pixelentpackung

- AXI4-Lite Slave-Steuerungsschnittstelle

RESSOURCEN-NUTZUNG

### **MVDK** Machine Vision Development

#### **MVDK-Beschreibung**

S2I MVDK (Machine Vision Development Kit) ist eine Hardwareplattform, die die Evaluierung und Entwicklung von Produkten basierend auf IP-Cores von S2I mit allen gängigen industriellen Vision-Schnittstellen vereinfacht. Die MVDK-Basiskarte bietet mithilfe von FMCs (FPGA Mezzanine Cards) umfassende Konfigurationsmöglichkeiten. Sie bietet eine Schnittstelle zu Vision-Sensoren und ermöglicht die Entwicklung von GigE Vision-, USB3 Vision- und CoaXPress-Kameras (Devices) sowie das Design von GigE Vision- und CoaXPress-Hosts.

#### Hardware und Referenzdesign

Das MVDK wird mit einem Enclustra Mercury FPGA-Modul und einer FMC-Schnittstellenkarte geliefert. Dazu gibt es ein vollständig funktionierendes Referenzdesign. Zusammen minimieren sie die Entwicklungszeit und ermöglichen beste Leistung mit geringem Platzbedarf und dennoch ausreichend Flexibilität zur Anpassung des Designs.

#### Für CoaXPress-Entwicklungen

Das für CoaXPress-Entwicklungen gelieferte MVDK umfasst eine FMC mit zwei oder vier CXP-6- oder CXP-12-Anschlüssen für das Device-Design (Kamera) oder Host-Design (Framegrabber). Die Device- und Host-Referenzdesigns sind vollständig mit CoaXPress konform.

#### Für USB3 Vision-Entwicklungen

Das für USB3 Vision-Entwicklungen gelieferte MVDK basiert auf der 5-Gbit/s-Technologie von USB3-Standardkomponenten und ermöglicht derzeit das kostengünstigste Design von Highspeed-Kameras.

Das USB3 Vision IP Core Development Kit ist vollständig mit GenlCam konform und von der A3 zertifiziert. Es bietet die einfachste Möglichkeit für den Einstieg in das Design einer neuen USB3 Vision-Kamera. Die USB3 Vision-Schnittstelle wird mit einer von S2I entwickelten FMC mit einem Cypress FX3 USB3-Chip implementiert.

#### Für GigE Vision-Entwicklungen

Das für GigE Vision-Entwicklungen gelieferte MVDK unterstützt die Entwicklung von Kamera- und Hostanwendungen, die mit der A3 GigE Vision-Spezifikation mit einer Geschwindigkeit von bis zu 10 Gbit/ s konform sind. Für Anwendungen mit 2,5,5 und 10 Gbit/s ist ein NBase-T-FMC-Modul von S2I erforderlich.

#### Für Sony IMX-Entwicklungen

Das MVDK von S2I ist mit der IMX Pregius-Sensorserie von Sony kompatibel, einer weitverbreiteten hochwertigen CMOS-Serie von Imagern. S2I unterstützt diese Sensoren mit dediziertem IP-Core zum Lesen der Daten von den Sensoren sowie ihre Steuerung. Das Referenzdesign besteht aus dem IMX IP-Core mit einem GigE Visionkonformen Ausgang.

#### Für MIPI CSI-2-Entwicklungen

Das mit dem MIPI CSI-2 Receiver IP-Core gelieferte MVDK unterstützt das Design von Kameras mit den weitverbreiteten, hochwertigen Imagern, die mit dem Standard MIPI CSI-2 konform sind. Der IP-Core von Sensor to Image unterstützt das Lesen der Daten von den Sensoren sowie die Steuerung der Sensoren. Das Referenzdesign besteht aus dem MIPI CSI-2 Receiver IP-Core mit einem GigE Vision-konformen Ausgang.

### Anmerkungen

#### Weitere Informationen auf www.euresys.com/s2i